Short Course I – Emerging Technologies

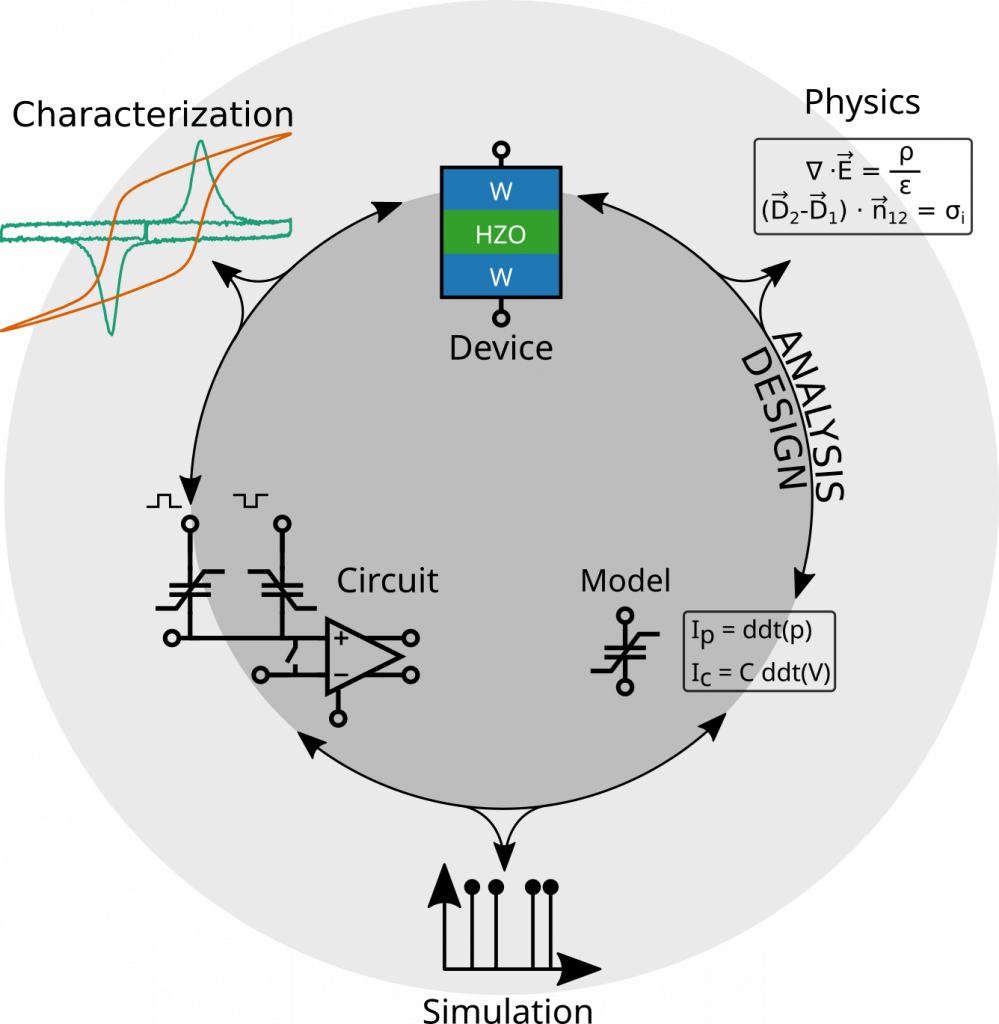

Design-Technology Co-Optimization for Reliable Integration of Emerging Memories in CMOS Circuits for Edge Computing

Erika Covi – Technical University of Munich

Edge computing architectures require real-time data processing with minimal latency under stringent power, area, and performance constraints. The heterogeneity of edge devices and the variability in the quality of processed data call into question the validity of traditional assumptions regarding computational fungibility. This necessitates the development of specialised hardware approaches that are optimised for efficiency at the network edge. Spiking neural networks (SNNs) offer appealing advantages for edge deployment through event-driven computation, low latency, and inherent energy efficiency. However, conventional CMOS-based digital and mixed-signal implementations are faced with fundamental limitations in terms of memory density, power consumption, and area overhead, which hinder their viability for edge computing specifications. Emerging memory technologies integrated at the back-end-of-line (BEOL) of CMOS processes present a promising solution. Operating at CMOS-compatible voltages with analogue conductance modulation capability, these devices enable in-memory computing architectures that mitigate the memory wall bottleneck by co-locating storage and computation. This approach facilitates the efficient hardware implementation of synaptic weights and neural dynamics, whilst concomitantly minimising data movement overhead. It is evident that there are still critical challenges to be addressed in order to achieve manufacturable, reliable edge computing systems. The integration of emerging devices with established CMOS flows introduces a complex process that must be managed with the utmost care. Device non-idealities, including cycle-to-cycle and device-to-device variability, endurance limitations, retention characteristics, and long-term reliability under operational stress conditions, directly impact system-level performance and require thorough electrical characterisation and modelling. Furthermore, the interdependencies between device physics, circuit design constraints, and algorithmic requirements demand rigorous design-technology co-optimization (DTCO) across the complete system stack. This presentation reports on experimental results from a tape-out integrating emerging memory devices with CMOS analogue circuits for edge computing. The present study demonstrates the critical engineering steps required for successful BEOL integration through comprehensive electrical characterisation of both individual devices and complete circuits. The present work demonstrates how concurrent development of device technology, circuit architectures, and algorithms is indispensable for the purpose of addressing integration bottlenecks, managing reliability concerns, and achieving system-level optimisation. The discussion encompasses practical trade-offs encountered during the design process, reliability considerations for ferroelectric devices in neuromorphic applications, and pathways towards manufacturable neuromorphic edge computing systems grounded in cross-layer co-optimization principles.

Erika Covi is an Assistant Professor at the Technical University of Munich (Germany), where she leads the Nanoelectronics Circuits and Systems (NCAS) Group. She received her Ph.D. in Microelectronics from the University of Pavia (Italy) in 2014. Following her doctoral studies, she was a researcher at the National Research Council (CNR) of Italy and Politecnico di Milano (Italy). She was later Senior Scientist at NaMLab gGmbH in Dresden, Germany, and Assistant Professor at the University of Groningen (the Netherlands). Her research focuses on the intersection of emerging memory devices, circuit design, and brain-inspired computing, with an emphasis on design-technology co-optimization (DTCO). Her work explores how the intrinsic physical properties of novel memory technologies can be leveraged to develop energy-efficient computational systems by integrating emerging memory devices with CMOS circuits. She has been awarded with the ERC Starting Grant in 2021 and the ERC Proof of Concept in 2025.

Two-Dimensional FETs for Logic and Beyond: Scaling, Integration, and New Computing Paradigms

Saptarshi Das – Pennsylvania State University

Two-dimensional (2D) semiconductors have emerged as a compelling platform for extending field-effect transistor (FET) scaling while simultaneously enabling new computing paradigms beyond conventional CMOS. In this tutorial, I present a device-to-system perspective on 2D FET technologies, drawing on three recent demonstrations from my group that span logic, scaling, and in-memory computing. I first discuss complementary 2D transistor integration through a monolithic one-instruction-set computer, highlighting how wafer-scale 2D CMOS can support non-traditional architectures with minimal hardware overhead. I then examine aggressively scaled MoS₂ FETs with sub-35 nm channel and contact lengths, focusing on electrostatics, contact engineering, and the implications for ultimate logic scaling. Finally, I present large-scale crossbar arrays based on three-terminal MoS₂ memtransistors, illustrating how 2D FETs can simultaneously serve as memory and computing elements for neuromorphic and probabilistic hardware. Together, these examples underscore how 2D FETs are not only viable replacements for scaled silicon devices, but also key enablers of tightly integrated logic–memory architectures and emerging computing models.

Dr. Das received his B.Eng. degree (2007) in Electronics and Telecommunication Engineering from Jadavpur University, India, and his Ph.D. degree (2013) in Electrical and Computer Engineering from Purdue University. He was a Postdoctoral Research Scholar (2013-2015) and Assistant Research Scientist (2015-2016) at Argonne National Laboratory (ANL). Dr. Das joined the Department of Engineering Science and Mechanics (ESM) at Penn State University in January 2016. Dr. Das received the Young Investigator Award from the United States Air Force Office of Scientific Research in 2017 and the National Science Foundation (NSF) CAREER award in 2021. Das Research Group at Penn State focuses on 2D microelectronics for monolithic 3D integration, bio-inspired sensing, neuromorphic computing, and hardware security.

Gate Stack Stability Challenges of Emerging MOS Device Technologies

Jacopo Franco – imec, Belgium

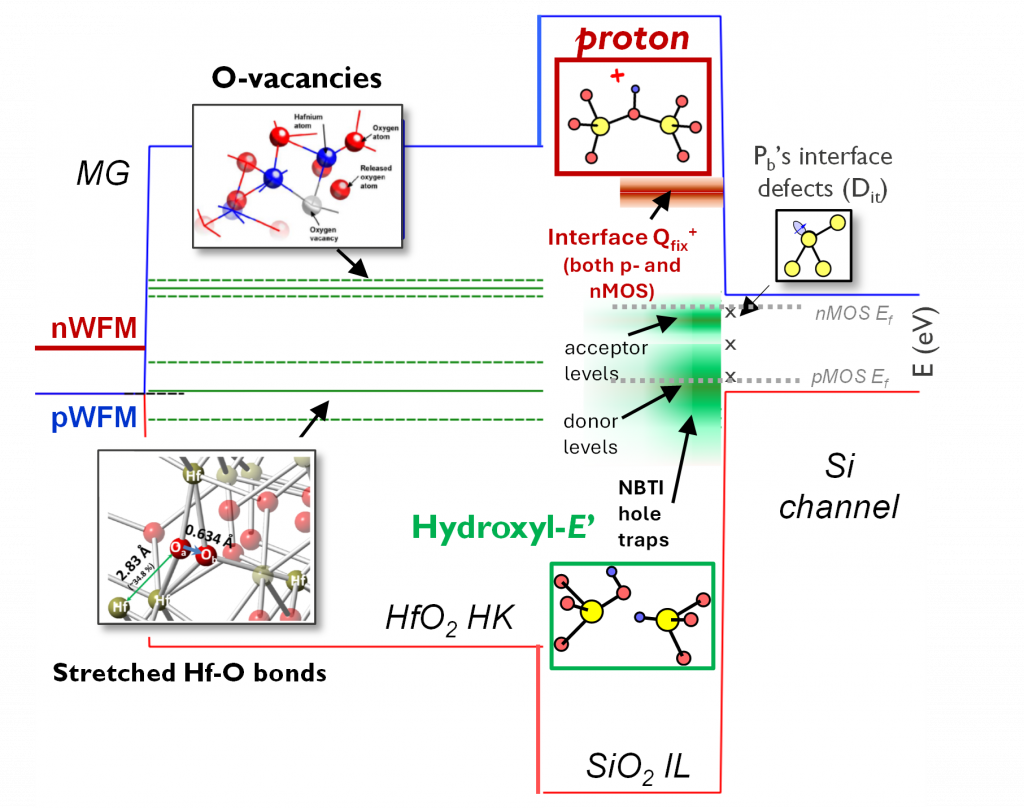

The unabated performance enhancement of semiconductor technology has been sustained in recent years by disruptive device and material innovations. For the successful deployment of any novel device concept, the promised enhanced performance must be guaranteed for the entire expected lifetime of the final product. Traditionally, device reliability optimization was an aspect considered only at a late stage in the development of a new device technology. We argue that in contemporary devices, fabricated with complex integrations and a plethora of materials, potential reliability issues should be considered from the very early stage of the technology development, as they can potentially disqualify otherwise promising device concepts. In particular, charge trapping in gate dielectrics is an aspect that can “make or break” any MOS-based device, and thus gate stack stability should be considered as a primary metric in the evaluation of novel device concepts. In this talk, we will review the fundamentals of charge trapping in gate dielectrics in terms of phenomenology, characterization techniques, and physical models. Next, we will briefly discuss, as case studies, some recent examples of MOS innovations which made it into mainstream technology (e.g., SiGe channels), as well as other examples which to date remain confined to academic research (e.g., III-V and Ge channels for Logic). We will then focus on specific gate stack challenges for upcoming CMOS technology innovations, including Nanosheet and Forksheet device architectures, and novel device concepts such as the stacked Complementary FET (CFET) and 2D channel transistors. Finally, we will discuss novel transistors based on oxide semiconductor channels (e.g., IGZO), which due to their extremely low off-state leakage and their flexible fabrication flow, are considered as potential gamechangers for memory periphery and, in general, for the heterogeneous integration of transistors in the Back End of Line (BEOL). For these devices, we will discuss how the interplay between their gate dielectric and channel instabilities makes the reliability assessment and optimization particularly complex, requiring a combination of electrical and optical characterization techniques.

Jacopo Franco is a Principal Member of Technical Staff in the Reliability group of imec, Belgium. He received the B.Sc. (2005) and M.Sc. (2008) from U. Calabria – Italy, and the Ph.D. degree from KU Leuven – Belgium (2013) in Electrical Engineering. His research focuses on CMOS FEOL reliability characterization, optimization, and modelling, and in particular: i) on gate stack development for novel device technologies (SiGe, Ge, III-V, IGZO), novel architectures (finFETs, FD-SOI, Nanowires, Nanosheets), and novel integration schemes (Sequential 3D tier stacking, CFETs); ii) on characterization and physics-based modelling of FEOL degradation mechanisms (BTI, Hot Carrier, Off-state degradation, TDDB, RTN, Time-Dependent Variability). He has (co )authored 300+ papers and 4 patent families, and he is a (co-)recipient of 8 IEEE awards. He has been serving in various functions on the Committees of IRPS, SISC, IIRW, ESREF, WoDiM and INFOS conferences, and as an Associate Editor of IEEE T-DMR and T-ED.

Resistive-switching RAM reliability from device to system

Cristian Zambelli – Università degli Studi di Ferrara

As the demand for high-performance, low-power non-volatile memory (NVM) grows, Resistive-switching Random Access Memory (RRAM) has emerged as a leading candidate for the next generation of Storage Class Memories (SCM). By bridging the performance gap between DRAM and Flash, RRAM offers the potential for high-speed operation, high-density integration via 4F² cross-point arrays, and low-power consumption. However, the path to widespread commercial adoption is complex, requiring a holistic understanding of reliability that spans from fundamental device physics to complex system-level management. This talk provides a comprehensive overview of RRAM reliability, focusing on Redox-based RRAM (OxRAM) using Hafnium oxide (HfO2) technology. At the device level, RRAM operation relies on the formation and disruption of a conductive filament (CF) composed of oxygen vacancies. While this mechanism enables high scalability, it is inherently stochastic. The choice of materials—such as amorphous versus poly-crystalline oxides—and the deposition chemistry (e.g., halide-based vs. metal-organic precursors) significantly influences the initial “Forming” process and the subsequent “Set” and “Reset” windows. We explore how the compliance current acts as a critical lever for controlling filament size, which in turn dictates the trade-off between power consumption and state stability. The core of RRAM reliability challenges lies in the dynamic nature of the conductive filament. We analyze the primary failure mechanisms: endurance, retention, and variability. Endurance is limited by the physical degradation of the oxide due to repetitive oxygen ion migration, where “Over-SET” or “Over-RESET” conditions can lead to permanent device wear. Retention, particularly at high temperatures, is threatened by the out-diffusion of vacancies, which causes the Low Resistance State (LRS) to drift toward a High Resistance State (HRS). Furthermore, we address the significant hurdle of variability, both device-to-device and cycle-to-cycle. This variability is compounded by phenomena such as Resistance Drift and Random Telegraph Noise (RTN), which pose severe risks to the stability of Multi-Level Cell (MLC) operations. To transition from a single cell to a functional system, these reliability “quirks” must be mitigated through architectural innovations. We discuss system-level strategies, including iterative program-and-verify algorithms to tighten resistance distributions and periodic content re-mapping to handle retention loss. The talk concludes by examining how these reliability considerations shape RRAM’s role in emerging applications. From automotive microcontrollers requiring extreme thermal stability to in-memory computing (IMC) architectures where RRAM serves as an analog synaptic weight, understanding the reliability chain from the atomic level to the system level is paramount for the future of emerging memory technologies.

Cristian Zambelli received the M.Sc. and the Ph.D. degrees in Electronic Engineering from the University of Ferrara, Ferrara, Italy, in 2008 and 2012, respectively. Since 2022, he holds an Associate Professor position with the same institution. His current research interests include the electrical characterization, physics, and reliability modeling of different nonvolatile memory technologies at the array level. He is also interested in the evaluation of the Solid-State Drives reliability/performance trade-offs exposed by the integrated memory technology and in neuromorphic computing using heterogeneous accelerators such as FPGAs and In-Memory Computing architectures.